ABSTRACT

The design of a low-power differential switched-capacitor amplifier for processing a fully-differential input signal coming from a pressure sensor interface is reported. The circuit is intended to amplify the input signal, convert it to single-ended mode and shift its output by an offset voltage. The gain and output offset voltage are digitally programmable. The differential switched-capacitor amplifier employs an op amp voltage cancellation technique without requiring its output to slew to analog ground each time the amplifier is reset. Additionally, the circuit topology is very insensitive to low op amp gain and allows to attain 9-bit linearity. Moreover, a switched-capacitor commonmode feedback configuration with symmetric loading of the differential mode loop has been adopted to reduce charge injection and leakage current errors as well as to settle much faster than traditional CMFB circuits. The circuit has been successfully integrated into a SoC device where, after the analog preprocessing, the pressure sensor signal is measured through a 10- bit ADC. Implemented in a standard 4-metal single-poly 0.25um CMOS process, the module occupies a silicon area of 0.115 mm2, operates down to 1.8V and its 3-V typical current consumption is 40uA.

1. INTRODUCTION

The continuous increase in System-on-Chip (SoC) complexity has been placing strong constraints to analog Intellectual Proprietary (IP) design. Although SoCs are usually targeted to digital-tailored technologies for financial reasons, they frequently demand lowpower low-voltage high-accuracy analog IPs. One way to overcome these conflicting requirements is the use of Switched-Capacitor (SC) circuits. Switched-capacitor technique efficiently compensates input offset and finite gain errors inherent to operational amplifiers (op amps). Moreover, due to its purely capacitive load, op amps do not require a high-power output driver, reducing area and power consumption as well as greatly simplifying frequency compensation as the load capacitance itself compensates the op amp. Finally, high accuracy and programmability are achieved with careful design and layout of capacitor ratios. The circuit presented herein is a low-power switched-capacitor amplifier implemented with metal (MiM) capacitors to achieve high linearity and device matching. Its architecture is described in Section 2 while Section 3 addresses its main design considerations. Experimental results are summarized in Section 4 followed by the final conclusions in Section 5.

2. CIRCUIT DESCRIPTION

Fig. 1 illustrates a block diagram of the Differential Amplifier (DA). It is composed by 2 stages. First stage amplifies the differential input signal by 16 allowing ±25% of digital trimming. The second stage is a differential-to-single-ended, unity gain stage that adjusts the DC output level by adding an offset voltage programmable within ±25% using 2 trimming bits. Both gain and offset trimming add active calibration capability to the Differential Amplifier through the 10-bit Analog-to-Digital Converter (ADC). Hence any deviations in gain and offset can be stored in internal SoC registers for later software compensation. The Differential Amplifier control signals (clock, enable, test enable and ADC trigger) properly synchronizes the circuit with the pressure sensor and the AD converter. The DA amplifies the input signal and adds an offset voltage to the output. Both gain and offset are functions of capacitor ratios. The mathematical description of the output voltage (derived from Fig. 2 and Fig. 5) is given by:

The design of a low-power differential switched-capacitor amplifier for processing a fully-differential input signal coming from a pressure sensor interface is reported. The circuit is intended to amplify the input signal, convert it to single-ended mode and shift its output by an offset voltage. The gain and output offset voltage are digitally programmable. The differential switched-capacitor amplifier employs an op amp voltage cancellation technique without requiring its output to slew to analog ground each time the amplifier is reset. Additionally, the circuit topology is very insensitive to low op amp gain and allows to attain 9-bit linearity. Moreover, a switched-capacitor commonmode feedback configuration with symmetric loading of the differential mode loop has been adopted to reduce charge injection and leakage current errors as well as to settle much faster than traditional CMFB circuits. The circuit has been successfully integrated into a SoC device where, after the analog preprocessing, the pressure sensor signal is measured through a 10- bit ADC. Implemented in a standard 4-metal single-poly 0.25um CMOS process, the module occupies a silicon area of 0.115 mm2, operates down to 1.8V and its 3-V typical current consumption is 40uA.

1. INTRODUCTION

The continuous increase in System-on-Chip (SoC) complexity has been placing strong constraints to analog Intellectual Proprietary (IP) design. Although SoCs are usually targeted to digital-tailored technologies for financial reasons, they frequently demand lowpower low-voltage high-accuracy analog IPs. One way to overcome these conflicting requirements is the use of Switched-Capacitor (SC) circuits. Switched-capacitor technique efficiently compensates input offset and finite gain errors inherent to operational amplifiers (op amps). Moreover, due to its purely capacitive load, op amps do not require a high-power output driver, reducing area and power consumption as well as greatly simplifying frequency compensation as the load capacitance itself compensates the op amp. Finally, high accuracy and programmability are achieved with careful design and layout of capacitor ratios. The circuit presented herein is a low-power switched-capacitor amplifier implemented with metal (MiM) capacitors to achieve high linearity and device matching. Its architecture is described in Section 2 while Section 3 addresses its main design considerations. Experimental results are summarized in Section 4 followed by the final conclusions in Section 5.

2. CIRCUIT DESCRIPTION

Fig. 1 illustrates a block diagram of the Differential Amplifier (DA). It is composed by 2 stages. First stage amplifies the differential input signal by 16 allowing ±25% of digital trimming. The second stage is a differential-to-single-ended, unity gain stage that adjusts the DC output level by adding an offset voltage programmable within ±25% using 2 trimming bits. Both gain and offset trimming add active calibration capability to the Differential Amplifier through the 10-bit Analog-to-Digital Converter (ADC). Hence any deviations in gain and offset can be stored in internal SoC registers for later software compensation. The Differential Amplifier control signals (clock, enable, test enable and ADC trigger) properly synchronizes the circuit with the pressure sensor and the AD converter. The DA amplifies the input signal and adds an offset voltage to the output. Both gain and offset are functions of capacitor ratios. The mathematical description of the output voltage (derived from Fig. 2 and Fig. 5) is given by:

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

Where (Vip - Vin) is the differential input voltage, VDD and VSS are the power supply voltages, (C1/C2) . (C4/C5) defines the amplifier gain and the term [1/2 - (C7/C5)] corresponds to the DC level shift at the output. The pressure sensor can be modeled as a resistive Wheatstone bridge with a differential output signal ratiometric to (VDD-VSS). Also, the ADC voltage reference is ratiometric to (VDDVSS). Therefore the DC level shifting at DA’s output is proportional to the power supplies as well (nominally 600mV when VDD = 3V and VSS = 0V). Both gain and offset capacitor array ratios can be adjusted by ± 25% around 16 and 0.2, respectively, during calibration process. Each DA stage compensates for op amp gain and op amp offset errors. Also, first stage has a high immunity to virtual ground (or analog ground) variations thanks to its fully differential architecture. The overall DA linearity is 9 bits (equivalent to the 10-bit ADC linearity). Due to its active calibration feature the Differential Amplifier gain accuracy has been set to 8 bits. However, noise floor in switches and capacitors is limited to 1/2 LSB within 10- bit resolution. In other words the DNL of the amplifying stage is 1/2 LSB at 10-bit resolution. Additional specifications of the circuit are: (a) power supply range from 2.1V to 3.6V; (b) input bandwidth of 100Hz; (c) DC input level at VDD = 3V: 1.5V ± 500mV; (d) sampling frequency of fclk = 125KHz; (e) temperature range from -40ºC to 125ºC; and (f) typical current consumption of 40uA.

3. CIRCUIT DESIGN

The switched-capacitor amplifier shown in Fig. 2 implements the gain stage cell and is the fully-differential counterpart of the amplifier presented in [1]. It is based on the Correlated Double Sampling (CDS) technique widely used to minimize errors due to finite offset voltages, 1/f noise, and finite op amp gain [2]. The CDS technique does not require a reset of the output in each clock phase, which alleviates the slew-rate requirements for the op amp. Also, as the non-ideal op amp effects are reduced, a more relaxed op amp specification for low frequency inputs can be attained. The ground reference AGND comes from the analog ground generator and typically is 0.5*(VDD-VSS). The classical feedback reset switch is replaced by the elementary sample-and-hold branches consisting of capacitors C3 and their associated switches.

During amplification phase (F2), sampling capacitors C1 discharge into C2 and the valid differential output is generated. This output is stored in C3. In the sampling phase (F1), capacitors C3 become the feedback capacitor while capacitors C1 sample the difference among the input voltages and the voltages at the opamp inputs (vp and vn nodes). At the same time, any offset voltage will be diferentially stored onto C2. In the next amplification phase, this offset voltage will be subtracted and cancelled. As the input signal bandwidth is much smaller than half the sampling frequency, i.e., the signal is significantly oversampled, Vop and Von do not vary much from one clock phase to the next. Thus, for a finite op amp gain (Av), the signal voltage at the inputs of the op amp is a slowly varying signal which is therefore nearly cancelled by the CDS switching of C1 and C2. This reduces the effect of finite op amp gain on the voltage gain of the stage. Detailed analysis of the fully-differential SC amplifier of Fig. 2 shows its DC gain is given by:

Eq. 2 shows that the voltage gain does not depend on capacitors C3 while the gain error is proportional to Av-2 rather than Av-1. This feature allows us to adopt a moderate-gain (~70dB) foldedcascode op amp without causing large errors in the amplifier gain. Besides reducing errors caused by op amp offset voltage and finite gain, the clock-feedthrough noise is also minimized by opening the switches connecting C3 to the op amp inputs (phase F1A) slightly before than closing the switches connecting C2 to analog ground (bottom plate sampling). Trimming capability is accomplished dividing each sampling capacitor in 3 sets (C1-1, C1-2 and C1-3) of unit capacitors (Cu) as long as C2 is also set to be equal to Cu. By default C1-1 = 12Cu and C1-2 = 4Cu define the sampling capacitor, so (C1/C2) = 16. By adding C1-3 = 4Cu to the sampling capacitor, the amplifier gain becomes 20 whereas taking off C1-2 from the default value, the gain is set to 12. The MiM capacitor size was initially estimated from maximum noise restriction but it provided a too small cap bound (1.45fF).

Being the DC amplifier gain determined by the capacitor ratio C1/C2, a proper matching level is needed to achieve an overall linearity of 9 bits. Such matching level set a minimum capacitor size. From mistmatch data for MiM capacitors in our CMOS process, it was estimated the minimum capacitor size to obtain a mistmatch error of 0.0894% (equivalent to have an effective number of bits - ENOB - of 10.128 bits). So, for such a capacitor size, Cu was obtained. Additionally, to limit noise injection from the substrate, the plates of all the capacitors tied to the op amp inputs were maintained in the top metal mask. The switch sizes were calculated based on the settling time error constraint. To get an error less than 0.5LSB for 10 bits, operating at a clock frequency of half clock frequency and taking into account a sampling capacitor of 16Cu, the minimum switch resistor value obtained using hand calculations was 100KOhms.

Then, it can be adopted devices with minimum geometries. Although, leakage imposes a channel length sligthtly higher than the minimum allowed. Fig. 3 illustrates the schematic of the op amp. It is a fullydiferential, folded-cascode, n-channel input transistors operational amplifier. One interesting feature about this opamp is its flexibility to be used either as a fully-differential or a single-ended amplifier. For single-ended applications, the inverted output terminal (OUTN) must be connected to the common-mode feedback input (CMC) which would normally be used by the common-mode feedback circuit to define the common-mode output voltage in fully-differential architectures. The use of low threshold voltage (Vth) transistors at the differential pair guarantees its operating voltage down to 1.7V. Typical electrical parameters for the op amp are 76dB open loop gain, 1.1MHz unit gain frequency with 69o phase margin, 11mA power consumption and output voltage swing ranging from VDD - 270mV to VSS + 230mV.

The SC common-mode feedback (CMFB) circuit is shown in Fig. 4. It employs a switched-capacitor configuration with symmetric loading of the differential mode loop [3]. The symmetric loading is obtained doubling the circuit in Fig. 4 and exchanging the clock phases. This guarantees that both sampling and setting of the common-mode output are simultaneously performed at every clock phase. Therefore the op amp common-mode output settles much faster than (almost twice as fast as) using the traditional CMFB topology. To guarantee the CMFB circuit properly settles in PVT (process, voltage and temperature ranges), the Differential Amplifier starts working at half the clock frequency and, after 32 cycles (512ms), the clock is reduced to fclk/8 to minimize op amp settling time errors. After the common-mode feedback circuit stabilizes, a commonmode signal will appear at the inputs of the opamp. Note the common-mode signal is close to the analog ground plus the opamp offset voltage. However, that fact does not cause any harmful effects since the op amp common-mode rejection ratio is adequate (144dB typical). Further, parasitic capacitances at the op amp input terminals have not effect on the gain; the impact of other stray caps is diminished as long as they are well matched; careful layout addressed the demand of maintaining similar parasitic capacitance along all the differential paths. Fig. 5 is the schematic of the differential to single-ended stage. It is based on the same SC CDS architecture adopted for the fullydifferential amplifier stage but adapted to be a single-ended unity gain amplifier. Neglecting op amp finite gain and input offset errors, the transfer function of the second stage is given by:

To allow the op amp to operate in a single-ended configuration, its inverted output was tied to the common-mode feedback terminal to self-bias the NMOS current sources. For unity gain both C4 and C5 equal 2Cu. The offset is introduced through C7 capacitor array and its respective switches. The offset capacitor size is adjusted to be one tenth of Cu. Note the offset trimming switches are connected either to VDD or VSS. The offset trimming is attained by properly choosing a specific charge transfer ratio between the offset capacitor array (C7) and the feedback capacitor (C5). By default, the offset trimming capacitor is set to 6Cu/10, so it gives an offset voltage at the output of 0.20*VDD. By adding Cu/10 to the offset trimming capacitor, the offset voltage will be 0.15*VDD whereas subtracting Cu/10 to that the offset voltage becomes 0.25*VDD. With such arrangement the output offset voltage of the Differential Amplifier can be trimmed by ±25% around 0.20*VDD. Additionally, it was necessary to design an analog ground generator, a current source for biasing all the circuits, and a clock generator that provides all non-overlapping clock phases necessary to drive the analog switches. As proper circuit operation derives from 2.5V control logic, digital level shifters were included as well.

4. EXPERIMENTAL RESULTS

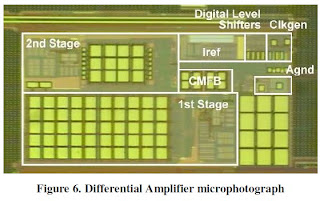

The Differential Amplifier has been integrated into a SoC realized in a standard 4-metal single-poly 0.25um CMOS process with metal-metal capacitors. Fig. 6 shows a microphotograph of the module with its main sub-blocks outlined. Clkgen stands for nonoverlapping multi-phase clock generator and Iref for current source. The module occupies a silicon area of 0.115 mm2 (480um x 240um) mostly due to large high-linearity capacitor arrays for achieving high accuracy on capacitor ratios. Silicon evaluation proved the module to be perfectly functional with very good overall performance such as: high linearity, high repeatability, low temperature sensitivity, high power supply rejection ratio and high input common-mode rejection ratio.

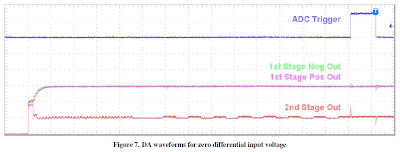

As the DA was designed to have its single-ended output sampled by an ADC, there is no access to its internal nodes during normal operation. In a SoC special operating mode, however, some critical nodes are routed to external pins so they can be monitored through the oscilloscope. This feature is achieved at the cost of higher noise injected by the chip into the module. Also the extra routing, bonding and probing in this operating mode add large capacitive loads into its switched-capacitor architecture demanding a slower switching clock and slightly degrading its performance due to leaky phase-to-phase charge transfer. Fig. 7 illustrates the DA measuring cycle in the SoC special operating mode for zero differential input voltage at 3V power supply. Horizontal and vertical scales are 400us and 0.5V respectively (except ADC trigger signal which is 2V vertical). 1st stage outputs remain at 1.5V while 2nd stage sustains a DC level as determined by the offset selection circuitry. At 80mV differential input, 1st and 2nd stages operate according to Fig. 8. It is apparent that a fast clocking rate is applied at the beginning. Although this short phase time does not allow for a proper settling time, all DA capacitors are rapidly charged. Once all nodes in the switched-capacitor architecture approach their steady state, the clock rate is reduced and subsequent phase cycles follow to precisely define its output. Since the voltages in a switchedcapacitor circuit reach steady state at the end of each phase, the clock is halted at the end of phase 2 (after a defined number of cycles) prior to triggering the ADC with a positive transition in the ADC trigger signal.

5. CONCLUSION

A low-power differential switched-capacitor amplifier for processing a fully-differential input signal coming from a pressure sensor interface has been presented. A SoC device integrating the amplifier has been realized in a 0.25um CMOS technology and silicon results proved the amplifier to be fully operational down to1.8V with 40uA typical supply current. Its very good overall performance derives from its high linearity, high repeatability, high power supply rejection ratio and high common-mode input rejection ratio.

Hernández Caballero Indiana

Asignatura: CAF

Fuente:http://www.freescale.com/files/technology_publications/doc/Papers/Eintell5342.pdf

No hay comentarios:

Publicar un comentario